# **User Guide**

For firmware version 1.5.1

# **Table of Contents**

|    | Introduction                                       |    |  |  |  |  |

|----|----------------------------------------------------|----|--|--|--|--|

|    | Hardware Connections                               |    |  |  |  |  |

|    | 1 USB Connection                                   |    |  |  |  |  |

|    | .2 Power Options                                   |    |  |  |  |  |

|    | .3 Minicard Types                                  |    |  |  |  |  |

|    | Expansion Headers                                  |    |  |  |  |  |

|    | Buttons/Switches                                   |    |  |  |  |  |

|    | .6 LED Indicators                                  |    |  |  |  |  |

|    | .7 Other Headers                                   |    |  |  |  |  |

|    | .8 Jumper Links                                    |    |  |  |  |  |

|    | Driver Installation and WISCE™ Support             |    |  |  |  |  |

|    | .1 WISCE™ Device Pack                              |    |  |  |  |  |

|    | .2 Minimum WISCE™ Version                          |    |  |  |  |  |

|    | .3 Controlling Lochnagar 2                         |    |  |  |  |  |

|    | 4 Lochnagar 2 Firmware Update                      |    |  |  |  |  |

|    | .5 Saving Lochnagar 2 Configuration to a Script    |    |  |  |  |  |

|    | Clocking                                           |    |  |  |  |  |

|    | 1 Configuring Clock Routing                        |    |  |  |  |  |

|    | .2 Clock Setup Guide                               |    |  |  |  |  |

|    | .3 Descriptions of Clock Sinks and Sources         |    |  |  |  |  |

|    | Digital Audio                                      |    |  |  |  |  |

|    | 1 Digital Audio Connection Diagrams                |    |  |  |  |  |

|    | .2 Configuring Digital Audio Routing               |    |  |  |  |  |

|    | .3 AIF Interfaces on Codec Minicard                |    |  |  |  |  |

|    | .4 AIF Interfaces on the Expansion Headers         |    |  |  |  |  |

|    | .5 PSIA Headers                                    |    |  |  |  |  |

|    | .6 S/PDIF and ADAT                                 |    |  |  |  |  |

|    | .7 Sound Card                                      |    |  |  |  |  |

|    | .8 Descriptions of Digital Audio Sinks and Sources |    |  |  |  |  |

|    | USB Audio Streaming                                |    |  |  |  |  |

|    | .1 CLUSBAudio Control Panel                        |    |  |  |  |  |

|    | .2 Using Lochnagar 2 with Windows WDM              |    |  |  |  |  |

|    | 3 Using Lochnagar 2 with WASAPI                    |    |  |  |  |  |

|    | 4 Using Lochnagar 2 with ASIO                      |    |  |  |  |  |

| 6. | .5 I2S Format on Lochnagar 2                       | 36 |  |  |  |  |

|    | 6 Lochnagar 2 USB Audio BCLK Rates                 |    |  |  |  |  |

|    | 7 USB MCLK                                         |    |  |  |  |  |

|    | I2S Mux                                            |    |  |  |  |  |

|    | .1 I2S Mux/Demux Operation                         |    |  |  |  |  |

|    | .2 Configuring the I2S Mux Peripheral              |    |  |  |  |  |

|    | .3 Clocking Restrictions                           |    |  |  |  |  |

|    | Analog Audio                                       |    |  |  |  |  |

|    | 1 Analog Port Connection Diagrams                  |    |  |  |  |  |

|    | .2 Configuring Analog Audio Routing                |    |  |  |  |  |

|    | 3 RCA Phono Input Ports                            |    |  |  |  |  |

|    | .4 Analog/Digital Microphones                      |    |  |  |  |  |

|    | .5 RCA Phono Output Ports                          |    |  |  |  |  |

|    | .6 Speaker Outputs                                 |    |  |  |  |  |

|    | .7 Analog I/O on the minicard                      |    |  |  |  |  |

| _  | GPIOs                                              |    |  |  |  |  |

| 9. | 5 1                                                |    |  |  |  |  |

|    | 2 GPIO Level                                       |    |  |  |  |  |

| 9. | .3 Lochnagar 2 On-Board GPIOs/LEDs                 | 49 |  |  |  |  |

# Lochnagar 2

| 9.4 GPIOs on Codec Minicards                            | 50 |

|---------------------------------------------------------|----|

| 9.5 Descriptions of GPIO Sinks and Sources              | 50 |

| 10 JTAG                                                 | 52 |

| 10.1 Required Chess toolchain update                    | 52 |

| 10.2 JTAG configuration                                 |    |

| 10.3 Custom JTAG Pin Configurations                     | 54 |

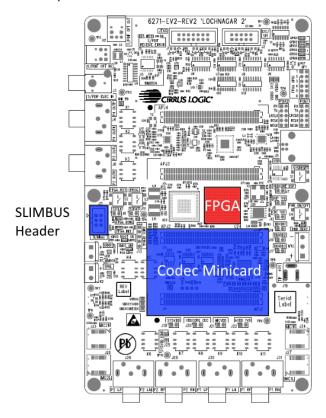

| 11 SLIMbus                                              |    |

| 11.1 SLIMbus Header                                     |    |

| 11.2 SLIMbus through Expansion Headers                  | 56 |

| 12 Power                                                | 57 |

| 12.1 Automatic Power Configuration                      | 57 |

| 12.2 Configuring Power Options                          | 57 |

| 12.3 MICVDD Options                                     |    |

| 12.4 VDDCORE Codec Options                              |    |

| 12.5 VDDCORE DSP Options                                |    |

| 13 Current Monitor                                      |    |

| 13.1 Lochnagar 2 Power Rails                            | 61 |

| 13.2 Current Monitor Plugin                             |    |

| 14 Example Setup Scripts                                |    |

| 14.1 WISCE™ Profile Scripts                             |    |

| 14.2 Lochnagar 1 and Lochnagar 2 Register Compatibility |    |

| 14.3 Details of Scripts Provided                        |    |

| 15 Troubleshooting                                      |    |

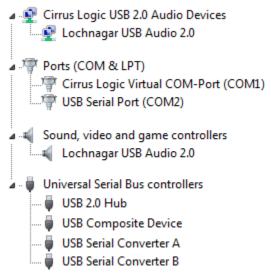

| 15.1 Lochnagar 2 Drivers in Device Manager              |    |

| 15.2 Common issues with Lochnagar 2                     | 68 |

| 16 Notices                                              | 73 |

### 1 Introduction

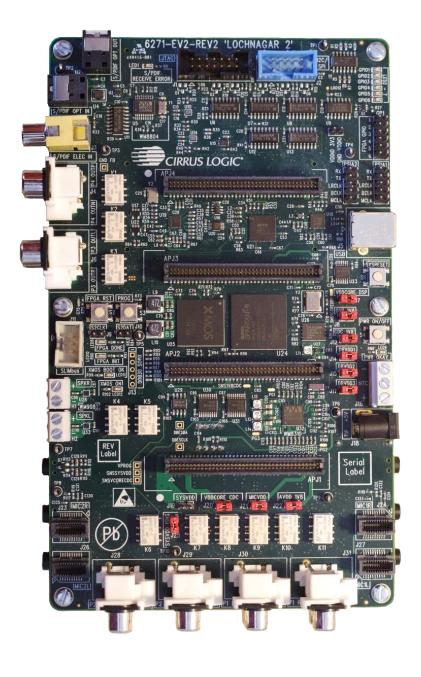

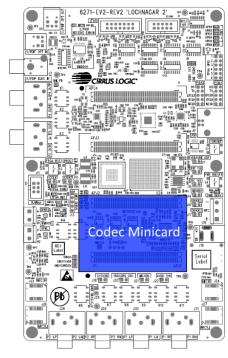

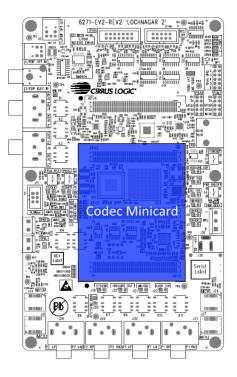

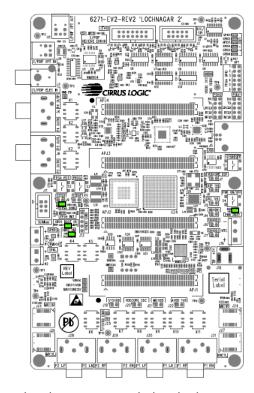

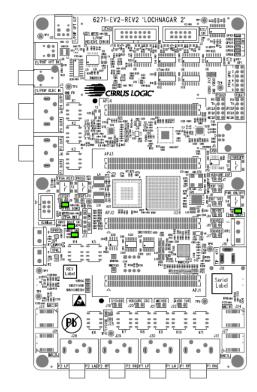

Lochnagar 2 (6271-EV2) is the next generation evaluation and development board for Cirrus Logic Smart Codec and Amps devices. It is designed to provide a variety of audio inputs and outputs to Cirrus Logic devices and to allow for configuration and programming them in a variety of possible use cases.

Lochnagar 2 is the same form factor as the original Lochnagar board and is compatible with the same Smart Codec and Amp minicards. It provides all the same functionality as the previous generation, and in addition adds many new features and capabilities. This includes the ability to stream up to 16 channels of USB audio, and a built-in current monitor feature that allows the power consumption of Cirrus Logic devices to be measured without any external equipment.

This document describes the features and usage of Lochnagar 2 in detail. The first two sections deal with the initial steps of hardware configuration and driver installation. Subsequent sections detail each of the features of the board and how to set it up in any potential use case. The final sections detail how to use the setup scripts provided with the Lochnagar 2 Device Pack and a guide on troubleshooting the board if any problems occur.

#### 2 Hardware Connections

#### 2.1 USB Connection

Lochnagar 2 is powered and controlled via a single USB connection. This provides:

- Power

- I2C/SPI communications to control device and board

- JTAG communications for DSP debug

- Multichannel USB streaming audio (USB class 2)

- USB serial port to communicate with Cirrus Logic devices with UART interfaces

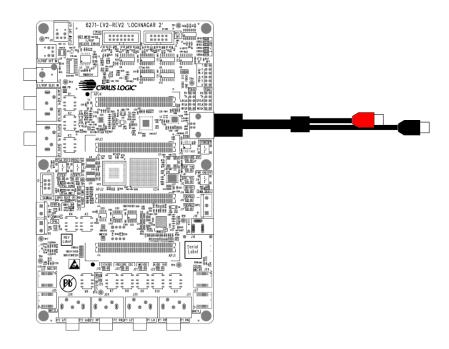

The board is provided with a Y-shaped USB cable, connecting a single USB B socket on Lochnagar 2 to two USB A ports on the computer (the black plug is for power and communications, the red for power only). Both USB connectors must be plugged in to allow for the power consumption of the board.

A Total Phase Aardvark connector is **NOT** required for Lochnagar 2 to operate, neither is a separate power supply required. All power and communications is provided to the board via this single USB link.

# 2.2 Power Options

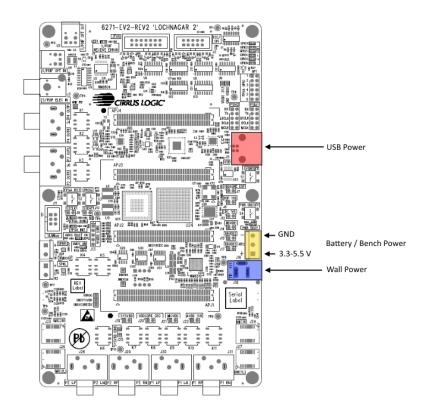

For most use cases, the provided USB cable is enough to power the entire board. In some scenarios, especially those using speakers, it may be necessary to plug a second power source into the Lochnagar 2 board. The onboard WM8310 PMIC will select the highest voltage from each of the three potential power supply inputs and use this to power the board's main SYSVDD bus. This is nominally 5V, but may be lower if a battery is used to supply the board.

#### 2.2.1 USB Power

As described in the <u>USB Connection</u> section, this is the normal mode of operation for the Lochnagar 2 board. For most use cases, USB power alone is adequate and there is no need to connect any additional power supplies to the board.

To be certain of getting the full 900 mA maximum input current supported by Lochnagar 2 USB connection, it is vital to ensure that a Y-shaped dual-USB cable is used and that both ends are plugged in at the PC end. If a USB hub is used, then it is also important to use a self-powered USB hub with a wall power connection, as otherwise it may not be able to supply enough current.

### 2.2.2 Wall Socket Supply

Lochnagar 2 provides a socket to accept 5V input from a dedicated wall supply.

It may be necessary to plug in the wall supply as well as the USB connector for more power-hungry use-case scenarios such as those involving speakers.

The wall power connector J30 is positive tip (tip = +5V), in contrast to the original Lochnagar board which used negative tip.

Protection diodes are fitted to prevent damage if a negative tip supply is inserted.

### 2.2.3 Battery/Bench Supply

Lochnagar 2 has three screw terminals which allow either a battery or a bench-top power supply unit to be plugged into the board.

It may be necessary to plug in a bench supply as well as the USB connector for more power-hungry use-case scenarios such as those involving speakers.

This input is nominally expected to be a 4.2 V battery, but the terminals can accept anything from 3.3 - 5.5 V. The terminals are marked with + and - symbols on the silkscreen to denote power and ground respectively.

Note that when the battery/bench supply is used as the sole power source for the board, the PWR ON/OFF button (S4) must be held down in order to power the board. This is in contrast to the other supply options, where the board will automatically power on as soon as the wall or USB connector are plugged in.

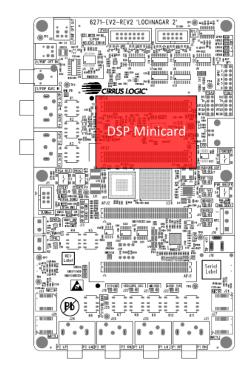

# 2.3 Minicard Types

Lochnagar 2 works with interchangeable minicards to allow for a variety of Smart Codec devices. The minicard connectors are fully backwards compatible with the original Lochnagar board.

Minicards should not be inserted or removed while the Lochnagar 2 board is powered. If using the wall socket or battery/bench screw terminals for board power, then it is recommended to fully disconnect or power down the external supply before changing minicards.

There are three main categories of minicard that can connect to Lochnagar 2.

**DSP Minicard**

**Codec Minicard (2-Header)**

**Codec Minicard (3-Header)**

#### 2.3.1 DSP Minicard

This type of minicard was designed for an older range of sidecar DSPs that sit alongside a codec minicard.

DSP minicards connect to the top two headers on the Lochnagar 2 board.

There are no current product lines that use the DSP minicard slot.

#### 2.3.2 Codec Minicard

Codec minicards house Cirrus Logic Codec and Smart Codec type devices. Smart Codecs include a built-in DSP, but are not classed as "DSP" minicards.

Traditionally, codec minicards connect to the lower two headers on the Lochnagar 2 board. However, some of the larger Smart Codec devices extend to the third header in order to make use of the extra I/O. These cards cannot be used alongside a DSP minicard.

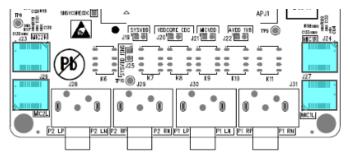

#### 2.3.3 Microphone Minicards

There are four microphone slots on the bottom of the Lochnagar 2 board.

These are designed to accept Cirrus Logic digital and analog microphone minicards.

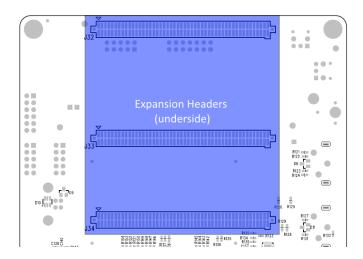

# 2.4 Expansion Headers

There are three expansion headers on the underside of Lochnagar 2, as shown in **Error! Reference source not found.**. T hese are designed to connect the board to other test hardware. They are commonly used to connect Lochnagar 2 to a Linux Application Processor system.

# 2.5 Buttons/Switches

There are four push buttons on the Lochnagar 2 board connected with power and reset functionality.

| Part Number | Name       | Description                                                                                                                                          |  |

|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| S1          | SYSRESET   | Resets all power rails on the board, returning all components to default state including Codec and FPGA                                              |  |

| S2          | FPGA RST   | Resets all FPGA registers                                                                                                                            |  |

| S3          | PROG       | Resets FPGA operation, forcing a reprogram from EEPROM<br>This will also reset all FPGA registers and re-initialize other<br>components on the board |  |

| S4          | PWR ON/OFF | Press when powered off: power on the board<br>Hold down for 2 seconds when powered on: power off the board                                           |  |

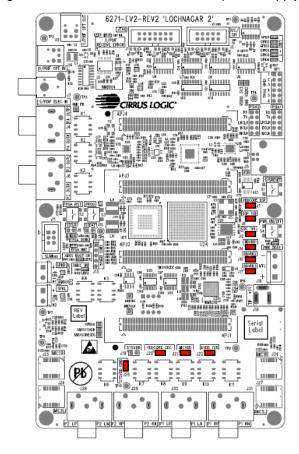

# 2.6 LED Indicators

There are six status LEDs on the Lochnagar 2 board that indicate the board's current state of operation:

| Part Number | Color | Name                 | Normally Lit? | Description                                                                                              |

|-------------|-------|----------------------|---------------|----------------------------------------------------------------------------------------------------------|

| LED1        | Red   | S/PDIF RECEIVE ERROR | No            | Set to red when there is an error receiving S/PDIF signals                                               |

| LED2-7      | Green | GPIO1 - GPIO6        | No            | Tied to FPGA GPIOs 1 to 6.                                                                               |

| LED8        | Green | FPGA DONE            | Yes           | Indicates that the FPGA booted successfully                                                              |

| LED9        | Green | PWR OK               | Yes           | Indicates the Lochnagar 2 board has power applied                                                        |

| LED10       | Red   | FPGA INIT            | No            | Indicates that the FPGA is currently initializing. Should flicker once upon board startup/power applied. |

| LED11       | Green | XMOS BOOT OK         | Yes           | Indicates that the XMOS USB transceiver chip booted correctly                                            |

| LED12       | Green | XMOS ON              | Yes           | Indicates that the XMOS USB transceiver chip is powered                                                  |

#### 2.7 Other Headers

There are several other headers on the Lochnagar 2 board that allow for connections to other systems.

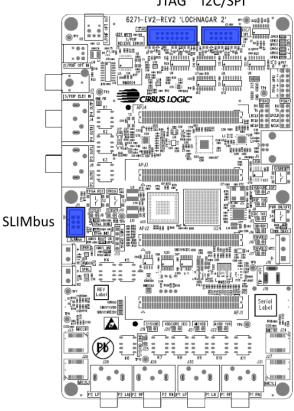

JTAG I2C/SPI

### 2.7.1 I2C/SPI (Aardvark)

Header J2 (I2C/SPI) is designed to connect to Total Phase Aardvark™ systems for legacy compatibility with the original Lochnagar board.

All I2C/SPI communications for most use cases are now expected to go through the standard USB link that also powers the board and provides USB audio streaming capability. However, the Aardvark can still be used for legacy applications or as a slave to test SPI master peripherals on the minicard.

#### 2.7.2 JTAG

Header J1 (JTAG) is designed to connect to Macraigor usbWiggler™ JTAG systems for legacy compatibility with the original Lochnagar board.

As with the I2C/SPI communications, JTAG functionality is now possible using the standard USB link that also powers the board and provides USB Audio streaming. It is still possible to use the Macraigor through this header if required. USB is the default option within the register map.

#### 2.7.3 SLIMbus

A 2x3 box header is provided to connect Lochnagar 2 to LnK SLIMbus test systems.

# 2.8 Jumper Links

Lochnagar 2 has replaced most of the jumpers from the original Lochnagar board with relay switches. All analog audio routing is now controlled via the FPGA register map.

There are 11 jumpers on the Lochnagar 2 board. These are all related to power supply rails.

These jumpers allow either the isolation of certain supply rails from the minicard, or the insertion of a series ammeter between the two pins in order to measure current consumption on individual rails.

No jumper should be fitted over J19 (SYSVDD), as this will prevent the built-in current monitor circuitry from working correctly.

| Header | Power Rail  | Jumper default                                                                                                                                    |                  |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| J7     | VDDCORE DSP | 0 V if no minicard connected<br>0.9 V / 1.2 V if minicard connected                                                                               | On (fitted)      |

| J8     | DSP 1V8     | 1.8 V                                                                                                                                             | On (fitted)      |

| J12    | CDC 1V8     | 1.8 V                                                                                                                                             | On (fitted)      |

| J14    | DBVDD1      | 1.8 V                                                                                                                                             | On (fitted)      |

| J15    | DBVDD2      | 1.8 V                                                                                                                                             | On (fitted)      |

| J17    | DBVDD3      | 1.8 V                                                                                                                                             | On (fitted)      |

| J19    | SYSVDD      | Alternative SYSVDD jumper connection bypassing the current sense circuitry. Should only be used if the current sense circuitry is causing issues. | Off (not fitted) |

| J20    | VDDCORE CDC | 0 V if no minicard connected<br>0.9 V / 1.2 V if minicard connected                                                                               | On (fitted)      |

| Header | Power Rail  | Default Voltage                                       | Jumper default |

|--------|-------------|-------------------------------------------------------|----------------|

| J21    | MICVDD      | 0 V default<br>1.8 V nominal when enabled             | On (fitted)    |

| J22    | AVDD 1V8    | 1.8 V                                                 | On (fitted)    |

| J25    | SYSVDD ISNS | Highest of Wall, USB and battery supplies Normally 5V | On (fitted)    |

Note that these power rail names refer to the rails on the Lochnagar 2 board and may not directly correspond to the rails on the device/minicard. This depends entirely upon the schematic designer of the codec minicard, and how they have decided is the best method to connect the DUT to the Lochnagar system. Always refer to the board schematics if there is any doubt.

(For example, recent codec minicards such as Moon CDB47L91-M-1 do not use the DBVDD1, DBVDD2, DBVDD3, AVDD\_1V8 rails, but instead derive all 1.8V rails from the single 1V8\_CDC supply rail on the Lochnagar 2 and split the rails on the minicard).

# 3 Driver Installation and WISCE™ Support

#### 3.1 WISCE™ Device Pack

In order to communicate with the Lochnagar 2 board, WISCE™ needs the Lochnagar 2 Device Pack to be installed. This automatically installs the following:

- Latest version of Lochnagar 2 board firmware; use the WISCE™ configuration plugin to start the update

- Lochnagar 2 configuration plugin for WISCE™

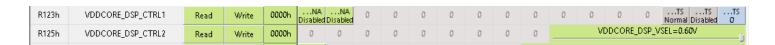

- Current Monitor plugin for WISCE™ to monitor current on selected supply rails

- Lochnagar 2 ASIO drivers for USB audio

- Lochnagar 2 SPI/I2C communications driver

- Register map description for WISCE™

- Sample WISCE™ configuration scripts for the board

### If upgrading...

It is advised to disconnect the board and close all audio streaming applications (eg. Adobe® Audition® or Foobar2000), terminal applications and JTAG debuggers before installing new versions of the Lochnagar 2 drivers. This ensures that nothing is attempting to communicate with the board during the driver installation process.

If an application is streaming audio or has an open connection to any of the drivers during the installation process, the driver installation will not be successful. The system will present itself as a "USB Composite Device" and attempts to automatically install the drivers will generate the error "This device cannot start. (Code 10)."

If this happens, the solution is to close all applications and re-install the Device Pack again from scratch.

#### 3.2 Minimum WISCE™ Version

WISCE™ 3.4.0.3 provides a minimum level of support for Lochnagar 2, but does not provide the full feature set. It is strongly recommended to use version **3.5.0.21** or above.

• The current stable release of WISCE™ is available from the Cirrus Logic website: http://www.cirrus.com/en/support/software/evaluationsoftware.html

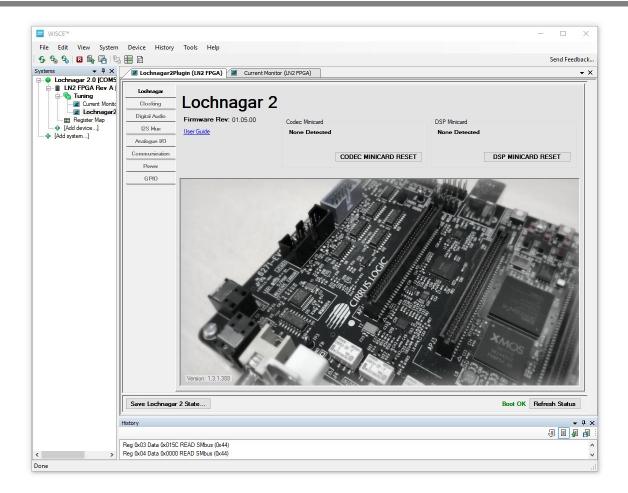

# 3.3 Controlling Lochnagar 2

Upon opening WISCE™, the Lochnagar 2 board should be automatically detected.

It will appear as a device called "LN2 FPGA" at I2C address 0x44. The LN2 FPGA device should have a "Tuning" folder that contains both the Lochnagar2Plugin and Current Monitor plugin. These allow for full configuration of the Lochnagar 2 board.

# 3.4 Lochnagar 2 Firmware Update

After installing the latest WISCE™ Device Pack (see section 3.1), restart WISCE™ and open the Lochnagar 2 Plugin.

# 3.4.1 Hardware Setup During Update

Firmware updates will generally work with most hardware minicards attached.

It is recommended to unplug any minicards, interposers or connectors that have their own separate power supplies during the Lochnagar 2 firmware upgrade process, as they may interfere with the process.

This includes:

- FPGA Emulation Interposers

- Zynq systems

- Amplifier minicards with separate power connections

### 3.4.2 Optional Update

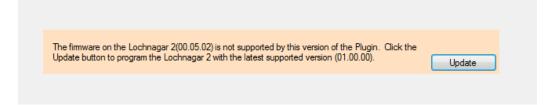

If the Lochnagar 2 firmware is not up-to-date, a yellow box prompting the user to update the board firmware will be displayed on the main page of the plugin:

# 3.4.3 Forced Update

If the version of firmware on the board is so old that the plugin/register map will not function at all, the plugin will remove the element of choice and will force the user to do an update before it can operate:

Firmware numbers in the screenshots are for illustration purposes only and may not reflect the behaviour of actual firmware releases.

# 3.4.4 Updating the Firmware

After clicking the "Update" button in the plugin, a prompt to reset the board and confirm that the user intends to do a board update is displayed. After confirming, it will take 2-3 minutes for the firmware update to complete.

It is important not to shut down WISCE $^{\text{\tiny{M}}}$  or power down or disconnect the Lochnagar 2 board during the firmware update process, as this may result in the Lochnagar 2 hardware becoming unusable.

# 3.5 Saving Lochnagar 2 Configuration to a Script

The Lochnagar 2 plugin now includes a feature that will save the full configuration of the Lochnagar 2 board as a WISCE™ text file that can be reloaded to bring the board back into exactly the same configuration. This WISCE™ profile script includes all the register sequencing required to set up the analogue paths.

To save the current configuration of the board as a WISCE™ profile script, click on the "Save Lochnagar 2 State..." button at the bottom of the plugin.

v1.5.1

### 4 Boot Procedure

#### 4.1 Boot Time

The exact boot time of Lochnagar 2 will vary depending on the version of firmware on the board, but is expected to be in the range of 2 to 5 seconds after applying power to the board. If the board is unresponsive or the SYS\_STS bit still returns the "Boot in Progress" status after this time period has passed, this indicates that the boot process has failed in some way.

# 4.2 Board LED Configuration

After a successful boot, the following LEDs should light up in the following order:

- LED9 (PWR OKAY)

- LED8 (FPGA DONE)

- LED12 (XMOS ON)

- LED11 (XMOS BOOT OK)

During this process the LED10 (FPGA INIT) should light up red with a quick flash, but should not remain on. The final expected LED configuration is shown below.

Any other configuration indicates that there has been an error during the boot process.

# 4.3 System Status Field

If any non-fatal errors happen that do not prevent communication with the board, an error code will be generated in the SYS\_STS field in the R0Bh (RESET\_CTRL1) register. This information is displayed in the bottom-right corner of the Lochnagar 2 Plugin along with a "Refresh Status" button that can be used to update the readback. This is the easiest way to read and interpret the system status.

Boot OK Refresh Status

The system status is always visible in the bottom-right corner of the Lochnagar 2 Plugin

From the register map view, the System Status field can be interpreted as follows. Each bit in the field has a different meaning, which allows different combinations of error messages to be present at the same time.

| SYS_STS Bit | RESET_CTRL1 Bit | Meaning                             |

|-------------|-----------------|-------------------------------------|

| 0           | 8               | 0 = Boot in Progress<br>1 = Boot OK |

| 1           | 9               | 1 = I2C Error                       |

| 2           | 10              | 1 = ID EEPROM Error                 |

| 3           | 11              | 1 = Power Config Error              |

### 4.3.1 Boot OK / Boot in Progress

This bit is set to 0 during the boot process and is only set to 1 upon successful completion. Some features of the Lochnagar 2 board (such as the analog routing features) will not operate correctly until the board has completed its boot procedure, so it is important to wait until Bit0 of the SYS\_STS field returns "Boot OK" before attempting to write to other areas of the register map.

Note that the Lochnagar 2 plugin may erroneously display the "Boot in Progress" message if WISCE's cache of the register map has not been refreshed for some reason.

#### 4.3.2 I2C Error

There was an error with the I2C bus on the device that prevented the board from booting correctly.

#### 4.3.3 ID EEPROM Error

There was an error parsing the data on the minicard's ID EEPROM. This may lead to problems with power rail configuration or SPI chip select configuration when using the connected minicard.

It may be possible to resolve this issue by manually configuring the Lochnagar 2 register map with the correct power and/or SPI chip select configuration data.

#### 4.3.4 Power Config Error

There was an error parsing or configuring the power rail configuration data stored on the minicard's ID EEPROM.

It may be possible to resolve this issue by manually configuring the Lochnagar 2 register map with the correct power configuration data.

# 5 Clocking

The Lochnagar 2 FPGA controls the clock routing on the board.

If no clock input is provided to the Cirrus device on the minicard, then it may not operate correctly. It is vital to configure the clocks on the Lochnagar 2 board before attempting to use the device.

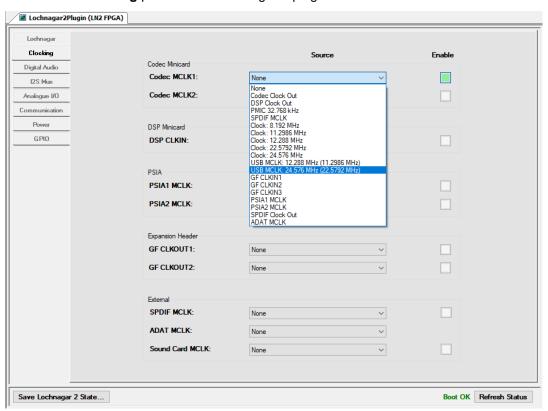

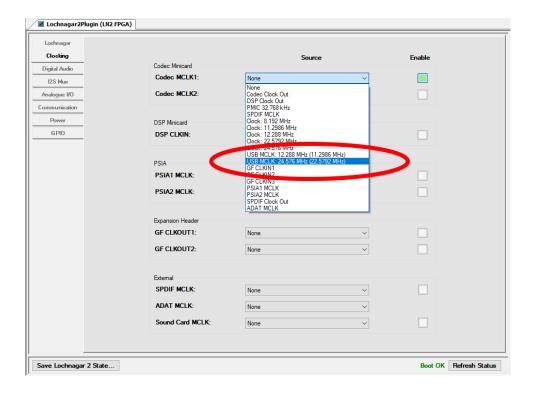

# 5.1 Configuring Clock Routing

Digital clock signals on Lochnagar 2 are routed through the central FPGA and can connect the clock signals on the board to a number of input sources.

Routing is controlled via the **Clocking** panel of the Lochnagar 2 plugin.

# 5.2 Clock Setup Guide

The Lochnagar 2 FPGA manages the clocking setup of various clocks on the board.

Clock signals are separated into clock sources (available clock frequencies from a variety of sources) and clock sinks (signals that require an input clock). The Lochnagar 2 allows the user to connect any clock source to any of the available clock sinks. There are some clocks that can be either source or sink, depending on the configuration. For example, if a PSIA header is used to connect the Lochnagar 2 to an Audio Precision test system, the Audio Precision can act as either MCLK master or slave, depending on the setup. Accordingly, Lochnagar 2 allows this clock signal to be used as either a sink or a source.

Lochnagar 2 has an on-board clock generator that generates the following frequencies: 11.2986 MHz, 12.288 MHz, 22.5792 MHz and 24.576 MHz. In addition, clocks can be provided from the USB streaming peripheral, PSIA headers, GF Expansion Headers, PMIC chip, clock output pins from the codec or DSP minicards, the S/PDIF transceiver or ADAT source.

When using digital audio with Cirrus Logic Smart Codec devices, the MCLK signal provided to the chip should be synchronous with any digital audio interfaces used on the chip. For example, if using the audio from the USB audio streaming, the MCLK provided to the slave device needs to be synchronous with the audio data coming from the USB audio streamer. For this reason, USB, PSIA, S/PDIF and ADAT MCLK signals are provided as available clock sources in the **Clocking** panel.

### 5.2.1 Example Configuration

To connect the USB MCLK signal to the Sound Card clock:

- 1. Open the Clocking panel of the plugin

- 2. Find the row associated with the Sound Card MCLK clock sink

- 3. Select USB MCLK: 24.576 MHZ (22.5792 MHz) Clock Source from the drop-down menu on the Sound Card MCLK row.

- 4. Click the enable button on the same row

This will provide the 24/22 MHz USB MCLK signal into the Sound Card peripheral.

# 5.3 Descriptions of Clock Sinks and Sources

#### 5.3.1 List of Clock Sinks

The following table lists all the potential destinations that clock signals can be routed to on Lochnagar 2. The register map addresses for the control registers associated with these clock sinks are provided for advanced users.

| Clock Sink      | Control Register | Description                                                               |  |

|-----------------|------------------|---------------------------------------------------------------------------|--|

| Codec MCLK1     | R1Eh             | Master clock input on the codec minicard                                  |  |

| Codec MCLK2     | R1Fh             | Master clock input on the codec minicard                                  |  |

| DSP CLKIN       | R20h             | Clock input on the DSP minicard                                           |  |

| PSIA1 MCLK      | R21h             | Master clock input or output signal on the PSIA1 pin headers              |  |

| PSIA2 MCLK      | R22h             | Master clock input or output signal on the PSIA2 pin headers              |  |

| GF CLKOUT1      | R24h             | Clock output to the GF expansion headers                                  |  |

| GF CLKOUT2      | R25h             | Clock output to the GF expansion headers                                  |  |

| SPDIF MCLK      | R23h             | Master clock input or output signal for the S/PDIF interface              |  |

| ADAT MCLK       | R26h             | Master clock input or output signal for the ADAT interface                |  |

| Sound Card MCLK | R27h             | Clock input signal to the Sound Card hardware on underside of Lochnagar 2 |  |

#### 5.3.2 List of Clock Sources

The following table lists all the potential sources of clock signals that can be routed to the clock sinks listed in the table above. The binary values for these sources are provided for advanced users.

| Clock Source Binary Value Description                  |      | Description                                                                 |

|--------------------------------------------------------|------|-----------------------------------------------------------------------------|

| None                                                   | 0x00 | No clock source selected                                                    |

| Codec Clock Out                                        | 0x01 | Clock output signal generated by the codec                                  |

| DSP Clock Out                                          | 0x02 | Clock output signal generated on the DSP minicard                           |

| PMIC 32.768 kHz 0x03 32.768 kHz clock generated by the |      | 32.768 kHz clock generated by the onboard power management IC               |

|                                                        |      |                                                                             |

| Clock: 8.192 MHz                                       | 0x09 | Fixed 8.192 MHz (16k multiple) clock from onboard clock generator chip.     |

| Clock: 12.288                                          |      | Fixed 12.288 MHz (48k multiple) clock from onboard clock generator chip.    |

| Clock: 11.2986                                         |      | Fixed 11.2986 MHz (44.1k multiple) clock from onboard clock generator chip. |

| Clock Source                                                                                                                                                                                                                                                             | Binary<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clock: 24.576<br>MHz                                                                                                                                                                                                                                                     | 0x07            | Fixed 24.576 MHz (48k multiple) clock from onboard clock generator chip.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Clock: 22.5792<br>MHz                                                                                                                                                                                                                                                    | 0x08            | Fixed 22.5792 MHz (44.1k multiple) clock from onboard clock generator chip.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| USB MCLK:<br>12.288 MHz<br>(11.2986 MHz)                                                                                                                                                                                                                                 | 0x12            | Use this clock input for USB streaming use cases Half rate clock that is synchronous to USB audio data. Frequency will depend on the sampling rate of audio being transferred over USB This will be either 12.288 MHz or 11.2986 MHz                                                                                                                                                                                                                                          |  |  |

| USB MCLK: 24.576 MHz (22.5792 MHz)  Use this clock input for USB streaming use cases Full rate clock that is synchronous to USB audio data. Frequency will depend on the sampling rate of audio being transferred over USB This will be either 24.576 MHz or 22.5792 MHz |                 | Full rate clock that is synchronous to USB audio data. Frequency will depend on the sampling rate of audio being transferred over USB                                                                                                                                                                                                                                                                                                                                         |  |  |

| GF MCLK1 0x0B Clock signal from the expansion headers on underside. Usually used when connected to Linux Application Processor systems                                                                                                                                   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| GF MCLK2 0x0D Clock signal from the expansion headers on underside. Usually used when connected to Linux Application Processor systems                                                                                                                                   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| GF MCLK3  0x0C  Clock signal from the expansion headers on underside.  Usually used when connected to Linux Application Processor systems                                                                                                                                |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| PSIA1 MCLK 0x0E Clock signal applied to PSIA1 headers (3.3V I2S pin headers)                                                                                                                                                                                             |                 | Clock signal applied to PSIA1 headers (3.3V I2S pin headers)                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| PSIA2 MCLK 0x0F Clock signal applied to PSIA2 headers (3.3V I2S pin headers)                                                                                                                                                                                             |                 | Clock signal applied to PSIA2 headers (3.3V I2S pin headers)                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SPDIF Clockout                                                                                                                                                                                                                                                           | 0x10            | Secondary clock output signal from the S/PDIF receiver chip. For advanced use cases only.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| ADAT MCLK                                                                                                                                                                                                                                                                | 0x11            | Clock signal from the ADAT receiver when used in ADAT mode.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| (ADAT MCLK<br>Only)<br>External ADAT<br>Clock                                                                                                                                                                                                                            | n/a             | This option in the drop-down menu does not set a value to ADAT_MCLK_SRC, but instead enables the ADAT_MCLK_ENA bit in the register map. This bit behaves differently for ADAT MCLK compared to the other clocks. When set, this mode uses a PLL to recover the incoming ADAT master clock from the optical cable. If any other value is selected in the drop-down, the ADAT_MCLK_ENA bit is unset and the source specified in ADAT_MCLK_SRC is used for the ADAT MCLK signal. |  |  |

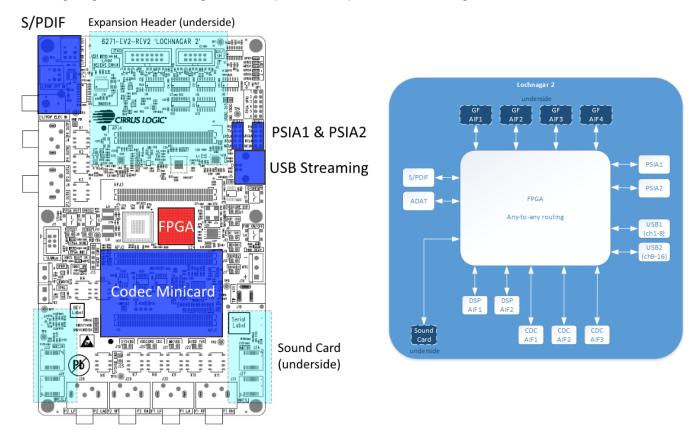

# 6 Digital Audio

This section details the digital audio inputs and outputs on the Lochnagar 2 board, and how to configure the routing. Any digital audio interface (AIF) on the Lochnagar 2 system can be connected to any other via the flexible routing of the FPGA.

# 6.1 Digital Audio Connection Diagrams

The following diagram details the digital audio inputs and outputs on the Lochnagar 2 board.

# **6.2 Configuring Digital Audio Routing**

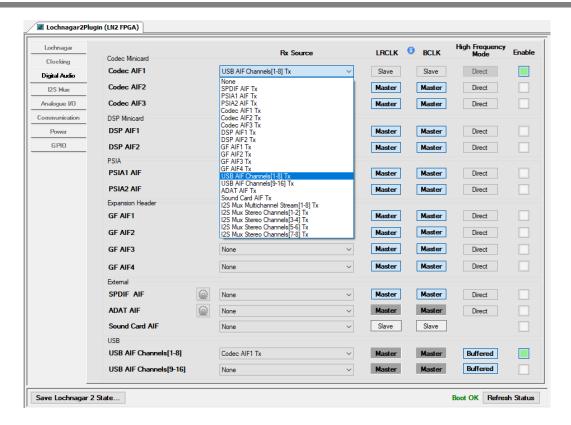

Digital audio signals on Lochnagar 2 are routed through the central FPGA and can connect any AIF port to any other AIF port on the board.

Routing is controlled via the **Digital Audio** panel of the Lochnagar 2 plugin.

# 6.2.1 BCLK/LRCLK Routing Operation

The Rx Source drop-down menu selects where the audio data comes from for the AIF sink on that row.

- If BCLK/LRCLK are set to Slave, the Lochnagar 2 board will supply the clocks from the audio interface selected in the Rx Source selection.

- If **BCLK/LRCLK** are set to **Master**, the Lochnagar 2 will not provide any clocks outputs to the AIF sink. The pins will be put into high-Z mode and used as inputs.

#### Clocks in Slave Mode

If BCLK and/or LRCLK for an AIF device are set to "Slave" mode, the Rx Source should not be set to "None", as this will mean that no clocks are provided to the AIF Slave device.

### 6.2.2 High Frequency Mode

Path delays in Digital Audio systems can cause problems when the round trip delay between the Digital Audio master and slave devices is comparable to the period of the bit clock. In these scenarios, the return data received by the master may be corrupted. Lochnagar 2 provides a buffered "High Frequency Mode" setting that will compensate for long round trip delays by introducing a single audio frame of buffering into the AIF master return data.

#### System level propagation delays must be taken into account.

High Frequency Mode is required when the Digital Audio bit clock is higher than 6.144 MHz and should allow correct operation for bit clocks up to 24.576 MHz in ideal operating conditions. As USB streaming on Lochnagar 2 is multichannel, it uses relatively high bit clock rates, so it is therefore recommended to set the High Frequency Mode to "Buffered" for all sampling rates above 24 kHz when using the USB streaming feature. The frequencies quoted are guidelines for ideal operating conditions, but several external factors on the PCB itself may add extra round trip delay. If margins are exceeded by external factors, High Frequency Mode may need to be enabled at a lower frequency than expected or may not be able to compensate at all. These external delay factors include high bus capacitance, large clock

to data propagation delays (> 15 ns) on the slave device, or minicards that have long PCB tracks or cabling.

The High Frequency Mode setting is only available on AIF peripherals where both BCLK and LRCLK are configured as AIF master.

There are two potential settings:

- Direct Mode = No buffering or delay is added onto this AIF signal by the Lochnagar 2 board

- Buffered Mode = A single audio frame of delay is introduced to the data received by this AIF master from the Rx Source.

Direct Mode is the default setting as it provides the lowest possible latency through the system. If audio corruption is observed at the AIF master, it is possible to resolve this by enabling the "Buffered" High Frequency Mode setting.

### 6.2.3 Example Configuration

To set up an AIF connection between the USB audio streaming and Codec AIF1 port:

- 1. Find the Codec AIF1 row on the **Digital Audio** tab of the Lochnagar 2 plugin.

- 2. Select an Rx Source for this audio connection. Choose USB AIF Channels[1-8] Tx to connect it to the USB streaming peripheral.

- Select whether Codec AIF1 is master or slave for the BCLK and LRCLK. Since USB streaming operates as master only, they must both be set to Slave in this example.

- 4. If audio is required in both directions, find the row for USB AIF Channels[1-8], and set the Rx Source to Codec AIF1 Tx. This will make the audio bidirectional.

- 5. If required, select the Buffered High Frequency Mode on the USB AIF Channels[1-8] row to add optional buffering into the return path. This may be required if the return data from the codec is corrupted due to path length delays.

- 6. Enable both interfaces using the buttons on the right of each row.

It is also important to make sure that the codec has an MCLK that is connected to a synchronous clock source. In this scenario, the **Clocking** panel of the plugin should be used to set MCLK1 or MCLK2 to the USB MCLK.

### 6.2.4 Advanced Clocking Configurations

Audio paths do not need to be set up directly between two AIF interfaces, and BCLK/LRCLK do not necessarily have to be driven by the same master or in the same direction, assuming that the Slave device also supports that mode. A single AIF master could potentially clock multiple slave devices by daisy-chaining the audio from one slave AIF port to the next.

This flexibility means that the Lochnagar 2 can be set up to emulate almost any potential AIF configuration in order to develop solutions or replicate problems.

Note that there is no protection for scenarios where the FPGA is configured incorrectly, so it is also important to make sure that the AIF interface connected to the FPGA is configured in the appropriate manner. If Codec AIF1 is set up as a Master on the Cirrus Logic Smart Codec device and also in the FPGA, the two devices will drive against each other on the line and potentially create mid-rail voltages.

#### 6.3 AIF Interfaces on Codec Minicard

The codec minicard supports up to three AIF interfaces (for smaller cards with two connectors) or five AIF interfaces (for larger cards that span over three connectors).

# 6.4 AIF Interfaces on the Expansion Headers

The expansion headers on the underside of Lochnagar 2 are designed to connect Lochnagar 2 to Linux Application Processor systems. The headers on the underside support up to four AIF interfaces.

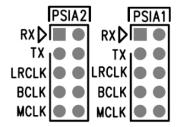

#### 6.5 PSIA Headers

The PSIA headers are designed to connect to Audio Precision testing equipment through the PSIA (Programmable Serial Interface Adapter) hardware.

This is essentially a standard I2S-based digital audio interface with 3.3V signal levels, consisting of the following signals:

- RXDAT (pin 1)

- TXDAT (pin 3)

- LRCLK (pin 5)

- BCLK (pin 7)

- MCLK (pin 9)

- Ground signals (pins 2, 4, 6, 8, 10)

The silkscreen markings on Lochnagar 2 will help the user determine which pin is which. Note that TX and RX directions are with respect to the external PSIA hardware, therefore the pin marked "RX" is an output from the FPGA.

#### Clocking

When using the PSIA with a Cirrus codec device, the codec can be used as either AIF clock master or clock slave. The **Clocking** panel of the Lochnagar 2 Plugin should be used to configure the MCLKs of the codec and PSIA ports appropriately.

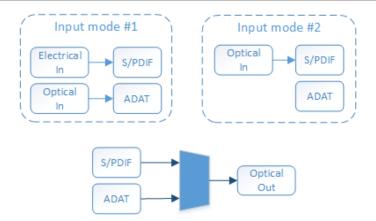

#### 6.6 S/PDIF and ADAT

There are S/PDIF optical and electrical input connectors on Lochnagar 2, and a single S/PDIF optical output connector. Lochnagar 2 also supports using ADAT protocol with the optical connectors.

#### **ADAT**

24

Lochnagar 2 only supports ADAT protocol with 48 kHz sampling rate, and it can only be used in I2S clock master mode.

#### 6.6.1 Standard Use Cases

- S/PDIF can be used with either electrical or optical input connector.

- ADAT can only be used with the optical input. If the optical input is already being used for S/PDIF, it cannot be used for ADAT.

There is only a single optical output, and can be used with either the S/PDIF or ADAT output.

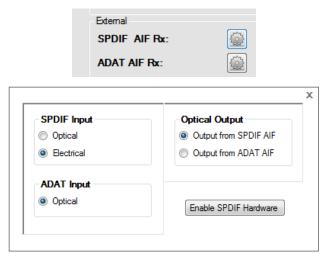

These configuration options can be selected within the **Digital Audio** panel of the Lochnagar 2 Plugin. Click the cogwheel-shaped "setup" icon next to either "SPDIF AIF Rx" or "ADAT AIF Rx" to bring up the S/PDIF and ADAT configuration options panel.

If using S/PDIF, it is important to click the "Enable SPDIF Hardware" button on this panel to bring the WM8804 S/PDIF transceiver chip out of reset.

### **Clocking**

When using S/PDIF or ADAT audio as clock masters with a Cirrus Logic codec device in slave mode, it is important that one of the codec's MCLK pins is connected to a clock source that is synchronous to the audio coming from the S/PDIF or ADAT source.

The **Clocking** panel of the Lochnagar 2 Plugin should be used to assign either MCLK1 or MCLK2 to one of the SPDIF MCLK or ADAT MCLK sources as appropriate.

#### 6.6.2 Advanced Use Cases

Lochnagar 2 also supports more advanced use case configurations using the WM8804 S/PDIF transceiver chip, including operating in clock slave mode. Since these require the additional configuration of the WM8804 chip, these modes cannot be enabled through the Lochnagar 2 plugin and are left for advanced users only.

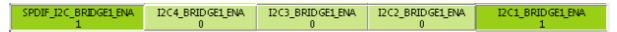

Firstly, the I2C bridge to the WM8804 chip must be enabled. This will connect the primary I2C bus on the system (I2C1) to the SPDIF I2C bus (SPDIF\_I2C):

The WM8804 should be placed into Software Control mode (SPDIF\_HWMODE = 0) and then taken out of reset (SPDIF\_RESET\_N = 1):

The WM8804 control interface can now be accessed over I2C and configured into a custom mode.

#### 6.7 Sound Card

There are 3 x stereo input 3.5 mm jacks and 3 x stereo output 3.5 mm jacks on the underside of Lochnagar 2. These comprise the "Sound Card".

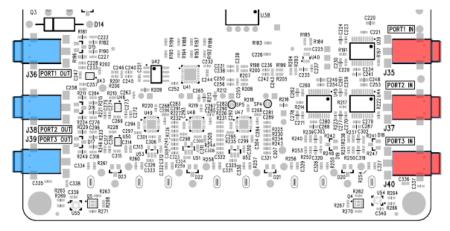

3.5 mm Jacks on underside of Lochnagar 2. Output Ports in Blue, Input Ports in Red

These inputs and outputs are not connected directly to analog ports on the minicard, but are presented as digital audio I/O within the **Digital Audio** routing panel of the Lochnagar 2 Plugin. Audio from any AIF port on the Lochnagar can be routed directly to the Sound Card.

#### 6.7.1 Sound Card Audio Format

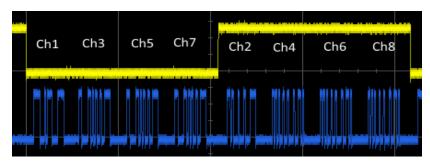

- The Sound Card expects to receive a 4- or 8-channel Multichannel I2S signal. This means the BCLK must be either 128 or 256 times the LRCLK rate (128Fs or 256Fs). If using 128Fs, channels 5 and 6 will not be available.

- Each sample should be supplied in a 32-bit wide slot, regardless of the audio word length. When 16- or 24-bit audio samples are used, zero-padding must follow so that 32-bits are used per sample.

- The Sound Card will always be the BCLK/LRCLK slave

- The Sound Card must be provided with a synchronous MCLK in the Clocking panel of the Lochnagar 2 Plugin.

The Sound Card requires the same multichannel I2S format as that generated by the USB streaming module.

The channels in the I2S stream will map directly to the 3.5 mm jacks as shown below.

| PORT1 left  | 1 |

|-------------|---|

| PORT1 right | 2 |

| PORT2 left  | 3 |

| PORT2 right | 4 |

| PORT3 left  | 5 |

| PORT3 right | 6 |

This channel mapping applies to both input and output ports. The data on channels 7 and 8 is discarded on the output side and zero-filled (silence) on the input side.

### 6.7.2 Enabling the Sound Card

The Sound Card is enabled within WISCE™ as follows:

- 1. Set up a clock source for the Sound Card MCLK on the Clocking panel and enable it

- 2. Set up the Sound Card as a source or sink within the Digital Audio panel

- 3. Click the enable button on the Sound Card row

### **Clocking**

The Sound Card always operates in clock slave mode. An Rx Source must be selected in order to supply BCLK and LRCLK signals.

In addition, the **Clocking** panel of the Lochnagar 2 Plugin should be used to assign an appropriate clock source to the Sound Card MCLK input. Without a synchronous MCLK input, the Sound Card will not function correctly.

# 6.8 Descriptions of Digital Audio Sinks and Sources

### 6.8.1 List of Digital Audio Sinks

The table below lists all the potential destinations that digital audio signals can be routed to on Lochnagar 2. The register map addresses for the control registers associated with these AIF sinks are provided for advanced users.

| Category                | Name                     | Control<br>Register | Description                                                                                                                                          |

|-------------------------|--------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Codec Minicard          | Codec AIF1               | R0Dh                | AIF1 port on the codec minicard                                                                                                                      |

| Codec Minicard          | Codec AIF2               | R0Eh                | AIF2 port on the codec minicard                                                                                                                      |

| Codec Minicard          | Codec AIF3               | R0Fh                | AIF3 port on the codec minicard                                                                                                                      |

| DSP / Codec<br>Minicard | DSP AIF1 / Codec<br>AIF4 | R10h                | How this interface is displayed in the plugin will depend upon your minicard May be either AIF4 on codec minicard or AIF1 on DSP minicard (obsolete) |

| Category                | Name                                   | Control<br>Register | Description                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSP / Codec<br>Minicard | DSP AIF2 / Codec<br>AIF5               | R11h                | How this interface is displayed in the plugin will depend upon your minicard May be either AIF5 on codec minicard or AIF2 on DSP minicard (obsolete)                                                                                                                                                                                                |

| PSIA                    | PSIA1 AIF                              | R12h                | PSIA pin headers for connection to Audio Precision PSIA or debug                                                                                                                                                                                                                                                                                    |

| PSIA                    | PSIA2 AIF                              | R13h                | PSIA pin headers for connection to Audio Precision PSIA or debug                                                                                                                                                                                                                                                                                    |

| Expansion Header        | GF AIF1                                | R16h                | Expansion header on underside of Lochnagar 2                                                                                                                                                                                                                                                                                                        |

| Expansion Header        | GF AIF2                                | R17h                | Expansion header on underside of Lochnagar 2                                                                                                                                                                                                                                                                                                        |

| Expansion Header        | GF AIF3                                | R14h                | Expansion header on underside of Lochnagar 2                                                                                                                                                                                                                                                                                                        |

| Expansion Header        | GF AIF4                                | R15h                | Expansion header on underside of Lochnagar 2                                                                                                                                                                                                                                                                                                        |

| External                | SPDIF AIF                              | R18h                | S/PDIF optical input/output Note: Basic use case is clock master only. If S/PDIF is used in clock slave mode, it will require extra configuration on the WM8804 S/PDIF transceiver chip to operate correctly. Note: S/PDIF requires extra configuration before it will operate. Click on the cogwheel 'setup' icon to select ADAT / S/PDIF options. |

| External                | ADAT AIF                               | R1Bh                | ADAT optical input/output Note: ADAT can be used in clock master mode only. If ADAT is in use, then S/PDIF will be limited to electrical input only. Note: ADAT requires extra configuration before it will operate. Click on the cogwheel 'setup' icon to select ADAT / SP/DIF options.                                                            |

| External                | Sound Card AIF                         | R180h               | Analog audio inputs and outputs through the 3.5 mm jacks on underside of the board. A clock supply must also be provided to the Sound Card before it will operate.                                                                                                                                                                                  |

| USB                     | USB AIF Channels[1-8]                  | R19h                | USB audio streaming ASIO channels 1-8 Note: USB streaming can only function in clock master mode                                                                                                                                                                                                                                                    |

| USB                     | USB AIF Channels[9-<br>16]             | R1Ah                | USB audio streaming ASIO channels 9-16  Note: USB streaming can only function in clock master mode                                                                                                                                                                                                                                                  |

| I2S Mux                 | I2S Mux Multichannel<br>Stream[1-8] Rx | R181h               | 8 channel I2S stream to the I2S Mux Converter block Note: This control is located on the I2S Mux Panel of the Lochnagar2Plugin                                                                                                                                                                                                                      |

| I2S Mux                 | I2S Mux Stereo<br>Channels[1-2] Rx     | R182h               | Channels 1-2 to the stereo to 8-channel conversion in the I2S Mux Converter block  Note: This control is located on the I2S Mux Panel of the Lochnagar2Plugin                                                                                                                                                                                       |

| I2S Mux                 | I2S Mux Stereo<br>Channels[3-4] Rx     | R183h               | Channels 3-4 to the stereo to 8-channel conversion in the I2S Mux Converter block Note: This control is located on the I2S Mux Panel of the Lochnagar2Plugin                                                                                                                                                                                        |

| I2S Mux                 | I2S Mux Stereo<br>Channels[5-6] Rx     | R184h               | Channels 5-6 to the stereo to 8-channel conversion in the I2S Mux Converter block Note: This control is located on the I2S Mux Panel of the Lochnagar2Plugin                                                                                                                                                                                        |

| I2S Mux                 | I2S Mux Stereo<br>Channels[7-8] Rx     | R185h               | Channels 7-8 to the stereo to 8-channel conversion in the I2S Mux Converter block Note: This control is located on the I2S Mux Panel of the Lochnagar2Plugin                                                                                                                                                                                        |

# 6.8.2 List of Digital Audio Sources

The table below lists all the potential sources of digital audio data that can be routed to the Digital Audio sinks listed in the table above. The binary values for these sources are provided for advanced users.

| Category                 | Name                           | Binary<br>Value | Description                                                                                                                                          |

|--------------------------|--------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | None                           | 0x00            | No audio source connected to this sink                                                                                                               |

| External                 | SPDIF AIF Tx                   | 0x01            | S/PDIF optical or electrical input                                                                                                                   |

| PSIA                     | PSIA1 AIF Tx                   | 0x02            | PSIA pin headers for connection to Audio Precision PSIA or debug                                                                                     |

| PSIA                     | PSIA2 AIF Tx                   | 0x03            | PSIA pin headers for connection to Audio Precision PSIA or debug                                                                                     |

| Audio Card               | Codec AIF1 Tx                  | 0x04            | AIF1 port on the codec minicard                                                                                                                      |

| Audio Card               | Codec AIF2 Tx                  | 0x05            | AIF2 port on the codec minicard                                                                                                                      |

| Audio Card               | Codec AIF3 Tx                  | 0x06            | AIF3 port on the codec minicard                                                                                                                      |

| DSP Card / Audio<br>Card | DSP AIF1 Tx / Codec<br>AIF4 Tx | 0x07            | How this interface is displayed in the plugin will depend upon your minicard May be either AIF4 on codec minicard or AIF1 on DSP minicard (obsolete) |

| Category                 | Name                                   | Binary<br>Value | Description                                                                                                                                                                       |

|--------------------------|----------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSP Card / Audio<br>Card | DSP AIF2 Tx / Codec<br>AIF5 Tx         | 0x08            | How this interface is displayed in the plugin will depend upon your minicard May be either AIF5 on codec minicard or AIF2 on DSP minicard (obsolete)                              |

| Expansion Header         | GF AIF1 Tx                             | 0x0B            | Expansion header on underside of Lochnagar 2                                                                                                                                      |

| Expansion Header         | GF AIF2 Tx                             | 0x0C            | Expansion header on underside of Lochnagar 2                                                                                                                                      |

| Expansion Header         | GF AIF3 Tx                             | 0x09            | Expansion header on underside of Lochnagar 2                                                                                                                                      |

| Expansion Header         | GF AIF4 Tx                             | 0x0A            | Expansion header on underside of Lochnagar 2                                                                                                                                      |

| USB                      | USB AIF Channels[1-8] Tx               | 0x0D            | USB audio streaming input (from PC) ASIO channels 1-8 Note: USB streaming can only function as clock master                                                                       |

| USB                      | USB AIF Channels[9-16]<br>Tx           | 0x0E            | USB audio streaming input (from PC) ASIO channels 9-16 Note: USB streaming can only function as clock master                                                                      |

| External                 | ADAT AIF Tx                            | 0x0F            | ADAT optical input.  Note: the ADAT hardware will need additional configuration  Click the cogwheel Setup icon to complete ADAT setup                                             |

| External                 | Sound Card AIF Tx                      | 0x10            | Analog inputs from the 3.5 mm jacks on the underside of Lochnagar 2  Note: an MCLK for the Sound Card must be configured in the clocking panel  For more details, see: Sound Card |

| I2S Mux                  | I2S Mux Multichannel<br>Stream[1-8] Tx | 0x11            | 8 channel I2S stream from the I2S Mux block Note: See I2S Mux panel to complete the setup                                                                                         |

| I2S Mux                  | I2S Mux Stereo<br>Channels[1-2] Tx     | 0x12            | De-muxed channels 1-2 from the 8-channel TDM to stereo I2S conversion in the I2S Mux block  Note: See I2S Mux panel to complete the setup                                         |

| I2S Mux                  | I2S Mux Stereo<br>Channels[3-4] Tx     | 0x13            | De-muxed channels 3-4 from the 8-channel I2S to stereo I2S conversion in the I2S Mux block  Note: See I2S Mux panel to complete the setup                                         |

| I2S Mux                  | I2S Mux Stereo<br>Channels[5-6] Tx     | 0x14            | De-muxed channels 5-6 from the 8-channel I2S to stereo I2S conversion in the I2S Mux block Note: See I2S Mux panel to complete the setup                                          |

| I2S Mux                  | I2S Mux Stereo<br>Channels[7-8] Tx     | 0x15            | De-muxed channels 7-8 from the 8-channel I2S to stereo I2S conversion in the I2S Mux block  Note: See I2S Mux panel to complete the setup                                         |

# 7 USB Audio Streaming

The Lochnagar 2 board presents itself as a USB audio device to the host PC using USB Audio Class 2 to transfer audio data.

### Do not reset or power down when streaming USB audio

If the Lochnagar 2 board is streaming USB Audio 2.0 when it is reset, the Windows audio drivers will stall. This is a common issue with Windows audio drivers when using external USB sound cards. When Lochnagar 2 is reconnected to the system, it may then fail to connect to WISCE due to the audio driver issues. In order to reconnect, the application playing USB audio to the Lochnagar 2 board must be stopped. If a failed attempt at connecting to WISCE™ has already occurred, the Lochnagar 2 board may need another reset in order to re-establish communications with the system.

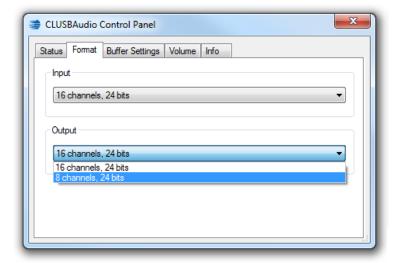

#### 7.1 CLUSBAudio Control Panel

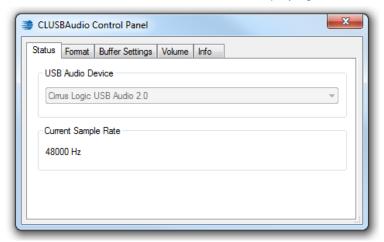

The CLUSBAudio Control Panel is for the Lochnagar 2 USB audio streaming system. A link to the panel can be found in the "Cirrus Logic" folder in the Start Menu.

The main **Status** tab of the CLUSBAudio Control Panel will display the Current Sampling Rate being used by Lochnagar 2. This is determined by either the Windows drivers setting (for DirectSound) or the audio software (for example Adobe Audition) for ASIO or WASAPI. This is useful for confirmation that audio is playing at the correct sampling rate.

The **Format** tab may be required for use cases where the sampling rate is 192 or 176.4 kHz. Due to limitations in bandwidth, Lochnagar 2 cannot support a full 16 channels of 24-bit audio at these sample rates, so the channel count must be reduced to 8 channels. On this tab, 'Input' refers to audio coming from Lochnagar 2 into the PC, and 'Output' refers to audio being transferred from the PC to Lochnagar 2.

For all other sampling rates:

• 16 channels, 24 bits (default recommended option)

For 192 kHz or 176.4 kHz:

• 8 channels, 24 bits

#### The format of the Input channels should match that of the Output channels.

For all use cases other than 192 kHz or 176.4 kHz sampling rates, it is recommended to keep these settings at the default value of 16 channels at 24 bits. Note that the input and output format selection made here will apply to the audio streaming device regardless of the audio drivers used (ASIO, WASAPI, DirectSound) so it is important to make sure this selection is correct if 192 kHz audio is to be played.

#### 192 kHz Mode

For 192 kHz and 176.4 kHz sampling rates, only the 8 channels / 24 bit mode will operate correctly. If 16 channels is used for either input or output, it will create bit-shifts (and therefore audible distortion) when WISCE™ is used at the same time as audio streaming. Both Input and Output settings must be set to 8 channel/24-bit mode in the CLUSBAudio Control panel. This is true regardless of whether you are using Windows DirectSound, WASAPI or ASIO drivers.

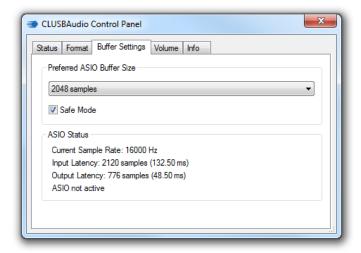

The **Buffer Settings** tab settings can be modified to provide a larger or smaller USB buffer, but be aware that some applications (e.g. Adobe Audition) may have problems with particular combinations of sample rate and buffer size. The "safe mode" setting provides extra tolerance for ASIO audio applications if they are not able to keep up with the audio demand at the expense of a slightly increased latency. It is recommended to keep this option enabled.

# 7.2 Using Lochnagar 2 with Windows WDM

Lochnagar 2 can act and function as a normal stereo USB audio device on a Windows system using Windows WDM drivers. Although Windows Vista introduced native support for WASAPI, which is technically superior, WDM is still the default audio driver for all Windows OS versions.

Stereo audio from standard Windows applications (Media Player, iTunes®, Spotify®, web browsers) can be routed through the Lochnagar 2 by simply selecting it as the default audio device on the system within the Control Panel.

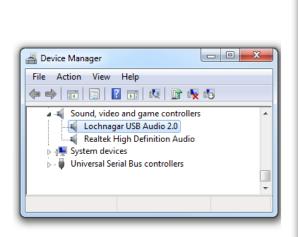

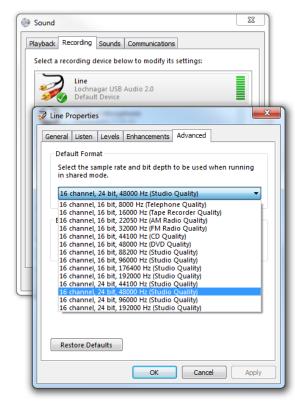

This has some limitations. Firstly, it only supports 2 channels, and all audio will be resampled by Windows to the sampling rate set within the Advanced panels of the "Speakers Properties" display (accessed by right-clicking on 'Speakers/Lochnagar USB Audio 2.0' in the window shown above). The input channels will operate at the rate set within the Advanced panel of the "Line Properties" display.

If the USB audio streaming is used for simultaneous playback and recording, the playback and record sampling rates must be set to the same value. It is also important to ensure that the format for the recording device matches the configuration of the CLUSBAudio panel in terms of number of channels and bit depth.

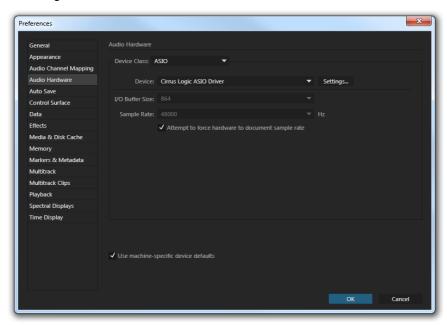

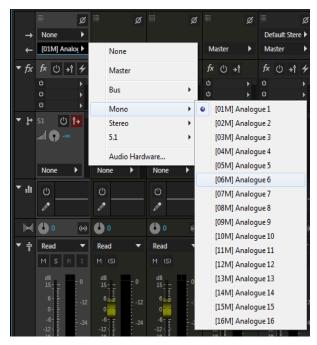

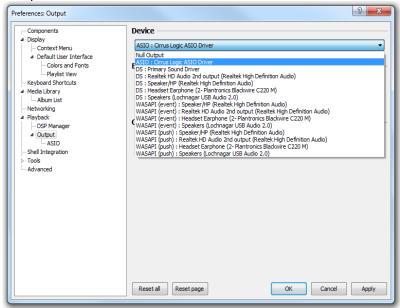

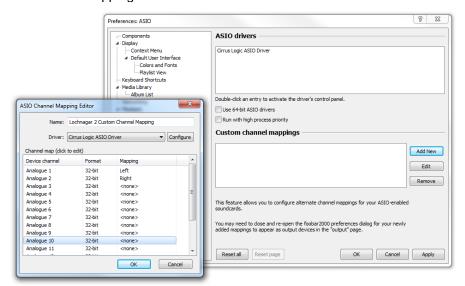

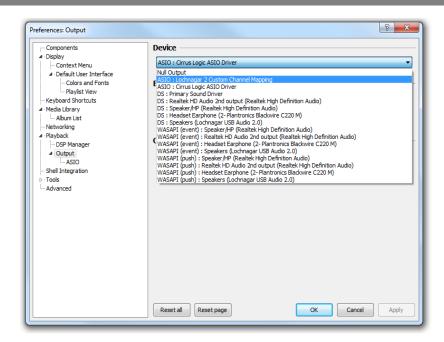

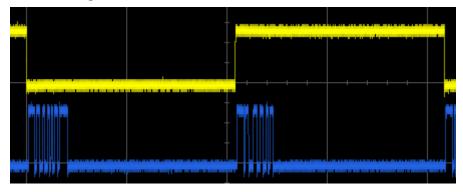

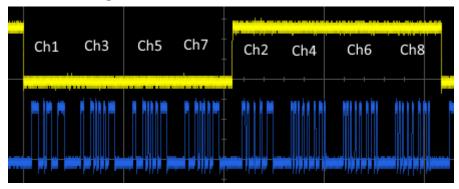

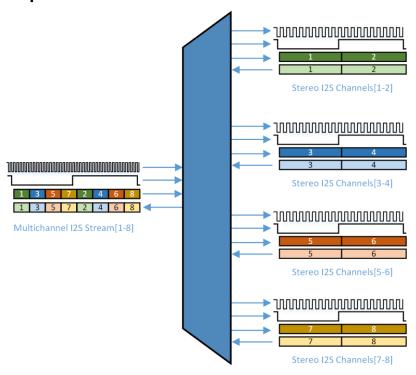

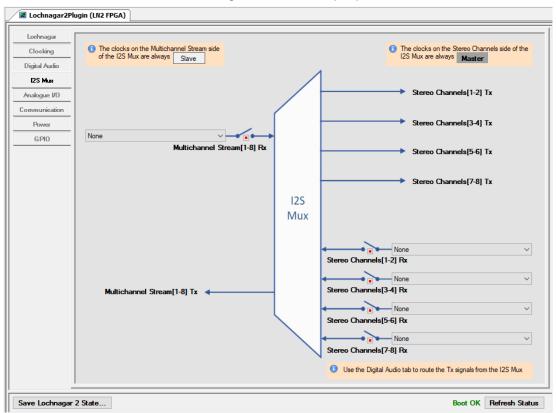

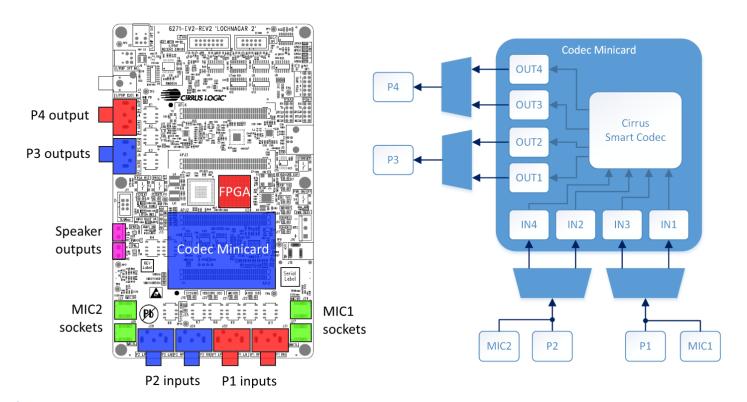

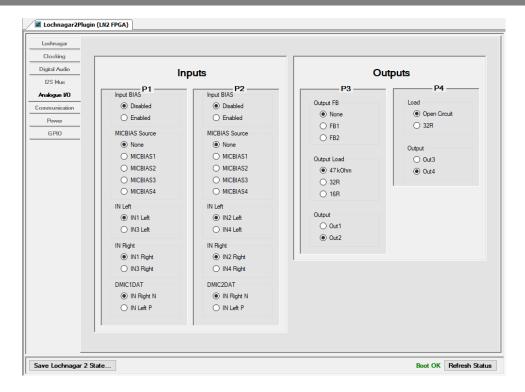

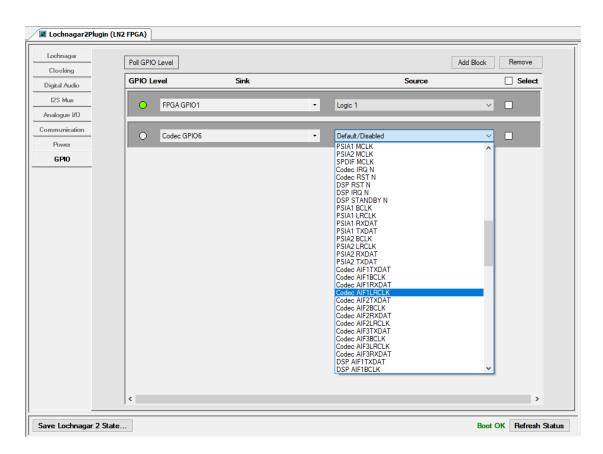

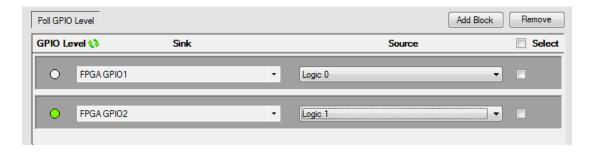

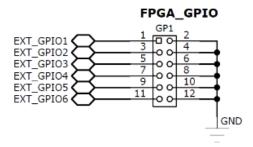

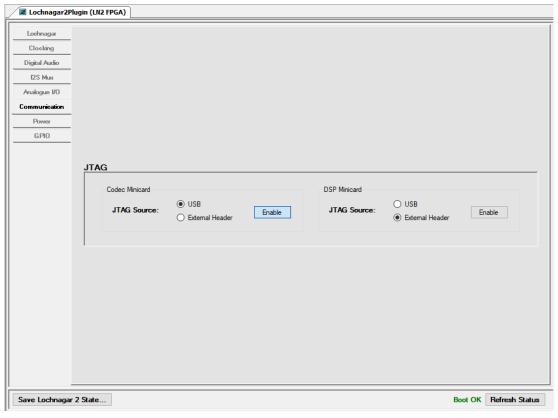

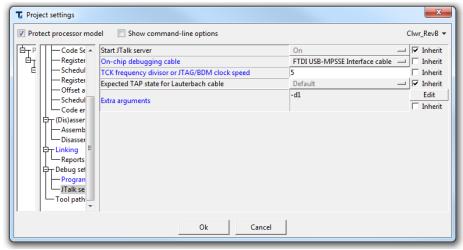

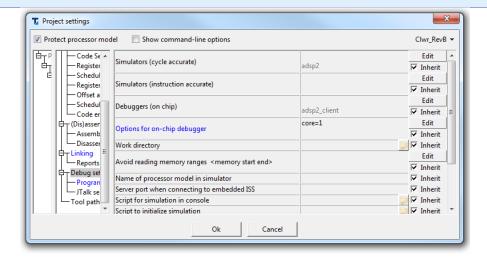

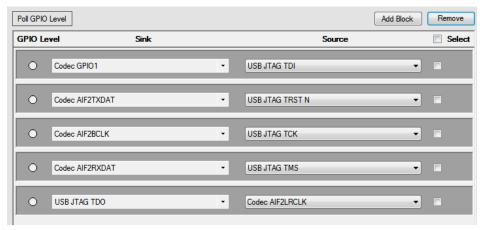

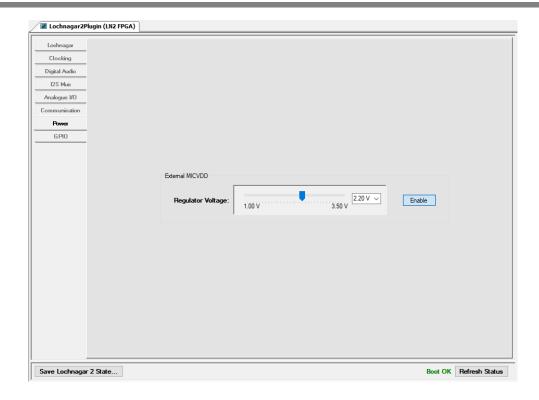

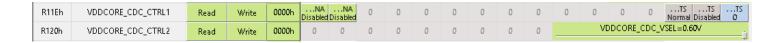

# 7.3 Using Lochnagar 2 with WASAPI